AMD confirma que sus aceleradores Instinct MI450 usarán tecnología de 2 nm de TSMC y prometen un 50 % más de memoria y ancho de banda

por Manuel Naranjo 1AMD ha dado una de esas confirmaciones que mueven agujas en la industria: la próxima generación de aceleradores para IA, Instinct MI450, se fabricará con tecnología de 2 nanómetros. Lo dijo Lisa Su en una entrevista con Yahoo Finance y, más allá del titular, la lectura es clara: la compañía quiere competir en la parte más dura del mercado, donde cuentan la densidad, la eficiencia por vatio y la capacidad real de producir a escala.

Qué ha confirmado exactamente

La frase de Lisa Su fue directa y sin adornos: el MI450 empleará el nodo de 2 nm “más avanzado” de su socio histórico TSMC. Ese dato encaja con lo que se viene filtrando desde el ecosistema: un diseño heterogéneo en el que el XCD (Accelerator Core Die) (el bloque de cómputo) salta al N2P de 2 nm, mientras que el AID (Active Interposer Die) y el MID (Media Interface Die) se quedan en N3P de 3 nm. Esta combinación no es caprichosa; permite reservar el nodo carísimo y complejo para la parte que mejor escala con transistores y mantener controlados el coste y el riesgo en los chips de soporte.

Por qué el salto a 2 nm importa (y qué letra pequeña trae)

Pasar a 2 nm no es un simple “rendimiento”: implica rendimientos de fabricación exigentes, empaquetado avanzado y un control térmico muy fino. El beneficio, si la cadena de suministro responde, está en la eficiencia por vatio y en la densidad de lógica que cabe en el mismo espacio.

Para IA, eso se traduce en más motores de cálculo, más rutas internas y menos cuellos de botella dentro del propio chip. La letra pequeña es que fabricar estos dispositivos exige interconexiones muy densas y un acoplamiento perfecto con memorias HBM; cualquier tensión en esos eslabones ralentiza los calendarios.

Memoria y ancho de banda: el arma que decide partidas largas

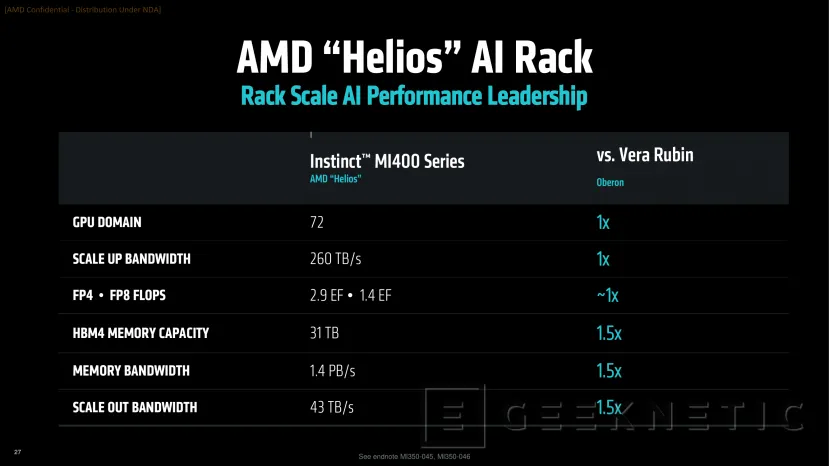

AMD ha deslizado la promesa que realmente puede mover contratos: rendimiento comparable en FP4/FP8 respecto a su competidor directo, pero con 1,5 veces más memoria y ancho de banda. En entrenamiento y despliegue de modelos grandes, lo que ahoga no son los teraflops, sino el muro de memoria. Más capacidad local y más velocidad de acceso implican menos offloading, menos tráfico a nodos vecinos y mejor escalado cuando el clúster crece. Aquí encaja, además, el rumor bien asentado de HBM4 de Samsung para MI450: no está confirmado por AMD, pero cuadraría con esa ambición de capacidad y caudal.

El rival al otro lado: Rubin, de NVIDIA

El enfrentamiento natural será con Rubin, la próxima plataforma de NVIDIA, prevista en N3P (3 nm). Sobre el papel, llevar el cómputo a 2 nm debería dar a AMD margen en eficiencia y densidad, pero esta carrera no se decide solo por el nodo. Pesan el software, la disponibilidad de HBM, la capacidad de empaquetado y, sobre todo, el suministro en volumen. Aun con esa prudencia, si el MI450 cumple con la memoria y el ancho de banda prometidos, habrá presión real en los pliegos de hiperescala donde hoy NVIDIA juega con ventaja.

Una hoja de ruta que alinea CPU y acelerador

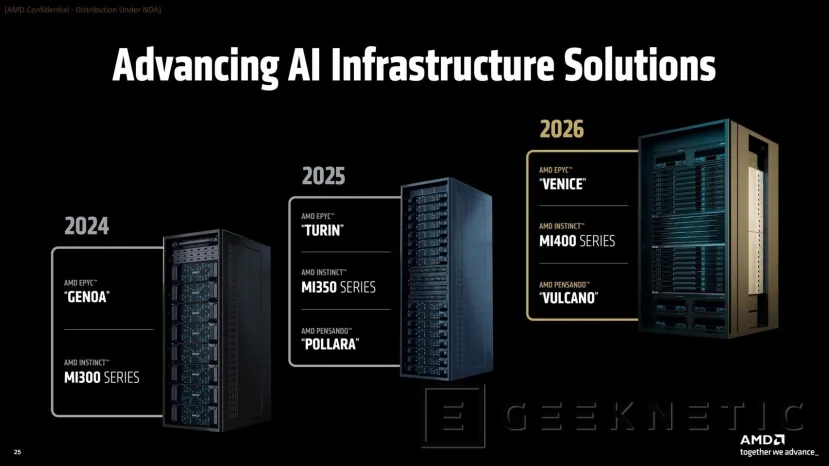

El movimiento no llega aislado. AMD planea usar el 2 nm de TSMC también en los EPYC “Venice” de próxima generación. Coordinar ciclos entre CPU y acelerador tiene sentido para los operadores: permite desplegar pods de IA con piezas que nacen pensadas para convivir, con perfiles térmicos y eléctricos más previsibles y con una ruta de actualización coherente.

Calendario y expectativas razonables

Con el año en la recta final y el CES 2026 asomando, el escenario más probable es una presentación de la serie Instinct MI400 en enero (y quizá un adelanto formal de Venice). Presentar no significa inundar el mercado al día siguiente: la disponibilidad de N2P, el suministro de HBM y la capacidad de empaquetado marcarán el ritmo real. Lo sensato es esperar pilotos y despliegues escalonados antes de un volumen amplio.

Qué cambia para quien opera centros de datos

Si las piezas encajan, MI450 puede aportar más trabajo útil por vatio, menos tráfico de datos “forzado” por falta de memoria local y mayor previsibilidad al escalar racks completos. Eso impacta el TCO de manera directa: menos energía para refrigerar, menos nodos para un mismo objetivo de entrenamiento y menos tiempo perdido en afinaciones defensivas. No es una promesa de milagros, es la suma de pequeñas eficiencias que, a gran escala, sí se notan.

Lo que todavía falta por saber

Quedan interrogantes importantes: la configuración final de HBM (tipo, capacidad por pila, velocidades), la envolvente térmica del sistema completo, los precios y plazos de entrega en volumen y el estado de las librerías y kernels para exprimir FP4/FP8 desde el día uno. Son los detalles que separan un buen anuncio de un producto que cambia inercias.

El Instinct MI450 es la jugada de AMD para competir donde más duele: nodo de 2 nm en el cómputo, memoria y ancho de banda por encima de lo habitual y una arquitectura que reparte inteligentemente los procesos de fabricación. Si la producción acompaña y el software llega afinado, 2026 puede ser el año en que la conversación pase de “quién tiene más FLOPS” a “quién alimenta mejor sus aceleradores”. Y en esa discusión, AMD se ha colocado en una posición que merece toda la atención.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!