La JEDEC publica el estándar JESD270-4 para memorias HBM4 con anchos de banda de 2 TB y chips de 64 GB

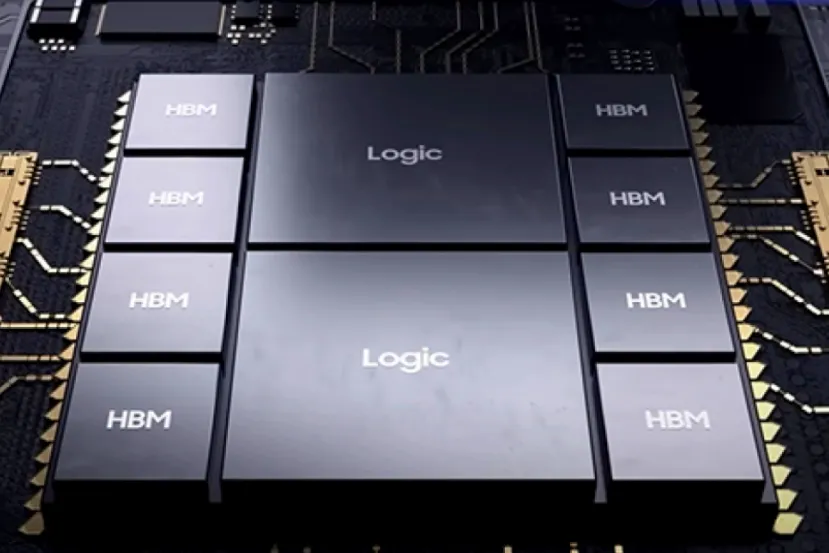

por Antonio DelgadoLa JEDEC, organización dedicada a la creación y desarrollo de los estándares de memoria y otros sectores de la industria, ha anunciado la publicación del estándar JESD270-4 para las memorias HBM4. Esta cuarta generación de memorias de alto ancho de banda se implementarán a gran escala en aceleradoras para Inteligencia Artificial y sistemas de cómputo de altas prestaciones o HPC.

El estándar para las memorias HBM4 e alcanza una velocidad de transferencia de datos de 8 Gbps por cada pin con una interfaz de 2.048 bits. También se duplica el número de canales independientes por cada apilado HBM4, pasando de 16 canales a 32 canales con dos "pseudo canales" cada uno. De esta forma, tenemos un ancho de banda máximo de 2 TB/s por cada módulo apilado de memorias HBM4.

Además, el estándar HBM4 permite apilados de hasta 16 capas, cada una de 32 Gb (gigabits) de capacidad, lo que permite crear apilados de 64 GB (gigabytes) de capacidad total por chip, aumentando la densidad de memoria en el mismo espacio. Adicionalmente, también soportan apulados de 4, 8 y 12 capas con chips de densidades de 24 y 32 bits.

Tras la publicación del estándar JESD270-4, es de esperar que no tardemos mucho en ver los primeros chips con HBM4 de nueva generación, dando un salto más en la evolución constante de los sistemas de cómputo de altas prestaciones y sus memorias RAM.

Fin del Artículo. ¡Cuéntanos algo en los Comentarios!